Overview

The CAN Controller IP Core is a synthesizable VHDL design that implements a complete Controller Area Network (CAN) 2.0A/2.0B compliant controller. It is designed to be integrated into FPGA-based systems and communicates to the user logic via FIFO style interface.

Features

- Compliant with Bosch CAN Specification 2.0 Part A and Part B

- Full support for CAN 2.0A (11-bit identifiers) and 2.0B (29-bit identifiers)

- Configurable bit timing via generics (prescaler, SJW, TSEG1, TSEG2, triple sampling)

- Works with external transmit and receive FIFOs

- Error handling, error frame generation, and status reporting

- 4 configurable ID filters can be set dynamically

- Field-proven on FPGA platforms (AMD/Microchip) through customer deployments

Hardware Validation

- PCAN-USB

- MCP25625

- STM32F3DISCOVERY

- Kvaser USBcan Pro 2xHS v2

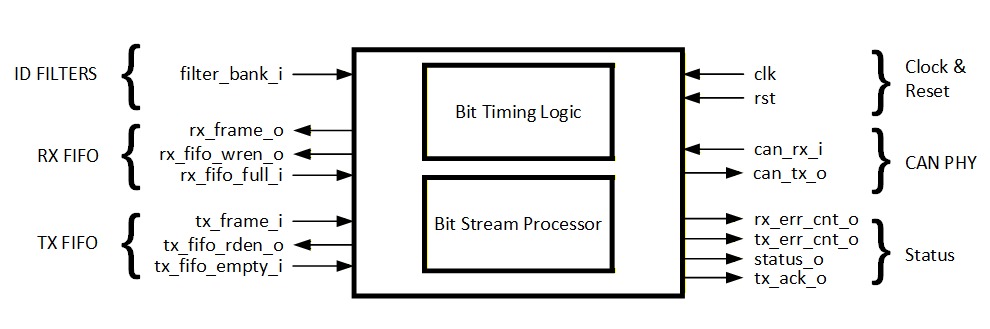

Interface

Resource Utilization

Table 1: MICROCHIP POLARFIRE SoC with Default Synthesis Configurations Libero SoC v2024.2

| 4LUT | DFF |

| 582 | 287 |

Table 2: AMD Artix Ultrascale+ with Default Synthesis Configurations Vivado 2023.2

| LUT | FF |

| 400 | 286 |

Deliverables

- Detailed Integration Guide: Clock/reset requirements, recommended FIFO selection, bit timing configuration examples, HW validated Vivado and Libero projects utilizing the IP

- Verification & Validation Package: Test summary, functional coverage snapshots, hardware validation evidence (logs/screenshots & live online demo per request)

For quotation requests, licensing options, and more information, please contact info@anadologic.com